# INTRODUCTION

This FLEX<sup>™</sup> Alphanumeric Decoder II date sheet describes the operation of the S5T8702.

The S5T8702 simplifies implementation of a FLEX<sup>™</sup> paging device by interfacing with any of several off-the-shelf paging receivers and any of several off-the-shelf host microcontroller/microprocessors. Its primary function is to process information received and demodulated from a FLEX radio paging channel, select messages addressed to the paging device and communicate the message information to the host. The S5T8702 also operates the paging receiver in an efficient power consumption mode and enables the host to operate in a low power mode when monitoring a signal channel for message information.

# **FEATURES**

- FLEX<sup>™</sup> paging protocol decoder

- 16 programmable user address words

- 16 fixed temporary addresses

- 16 operator messaging addresses

- 1600,3200,and 6400bps(bits per second) decoding

- Any-phase or single-phase decoding

- Uses standard Serial Peripheral Interface (SPI) in slave mode

- Allow low current STOP mode operation of host processor

- Highly programmable receiver control

- Real time clock time base

- FLEX fragmentation and group messaging support

- Real time clock over-the-air update support

- Compatible with synthesized receivers

- Low Battery Indication(External detector)

- 28 used pins (32-pin package standard)

- Internal demodulator and data slicer

- Improved battery savings via partial correlation and intermittent receiver clock

- Full support for revision 1.9 of the FLEX protocol

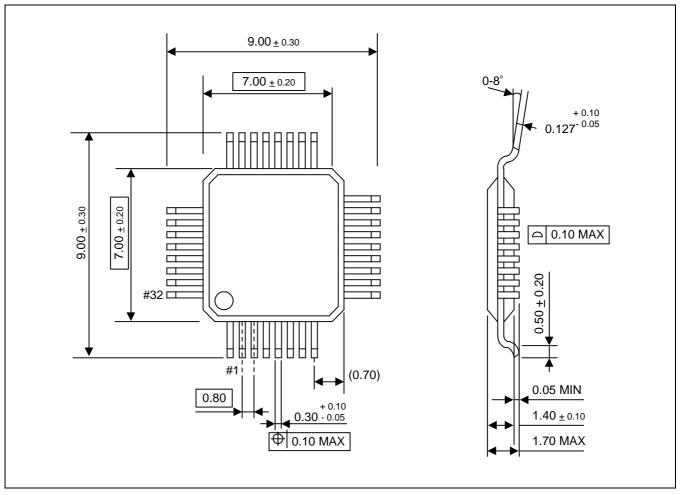

- 32-pin LQFP package

- Supply voltage: 1.8 to 3.6V

- Operating frequency: 76.8kHz or 160kHz

S5T8702

# **ORDERING INFORMATION**

| Device Name      | Package Type | Operating Temperature |

|------------------|--------------|-----------------------|

| +S5T8702X01-E0R0 | 32-LQFP-0707 | -25°C to 85°C         |

+: New Product

# SYSTEM BLOCK DIAGRAM

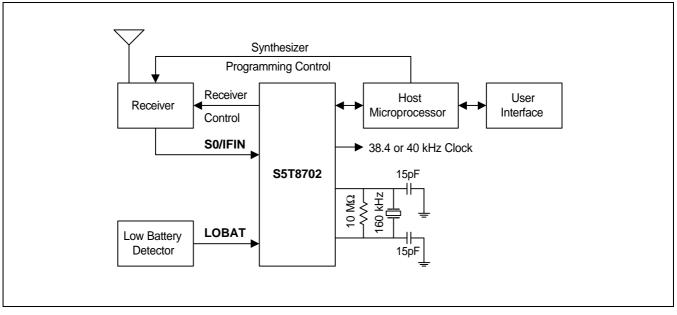

Figure 1 : Example Block Diagram Using Internal Demodulator

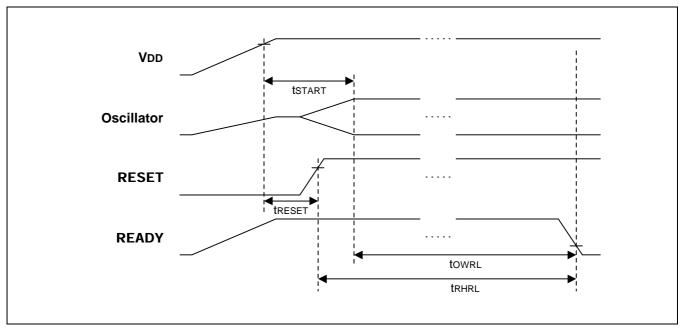

When configured to use the internal demodulator, the S5T8702 connects to a receiver capable of generating a limited (i.e. 1-bit digitized) 455kHz or 140kHz IF signal. In this mode, the S5T8702 has 7 receiver control lines used for warming up and shutting down a receiver in stages. The S5T8702 has the ability to detect a low battery signal during the receiver control sequences. It interfaces to a host MCU through a standard SPI. It has a 1minute timer that offers low power support for a time of day function on the host.

When using the internal demodulator, the oscillator frequency (or external clock) must be 160kHz. The **CLKOUT** signal can be programmed to be either a 38.4kHz signal created by fractionally dividing the oscillator clock, or a 40kHz signal creating by dividing the oscillator clock by 4.

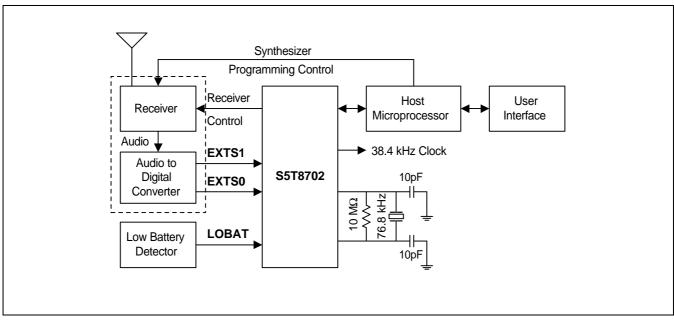

Figure 2 : Example Block Diagram Using External Demodulator

The S5T8702 can also be configured to connect to a receiver capable of converting a 4 level audio signal into a 2 bit digital signal. In this mode, the S5T8702 has a 8 receiver control lines used for warming up and shutting down a receiver in stages. It also includes configuration setting for the two post detection filter bandwidths required to decode the two symbol rates of the FLEX signal. Also when using an external demodulator, the oscillator frequency (or external clock) must be 76.8kHz and the **CLKOUT** signal (when enabled) is 38.4kHz clock output capable of driving other devices.

# FUNCTIONAL BLOCK DIAGRAM

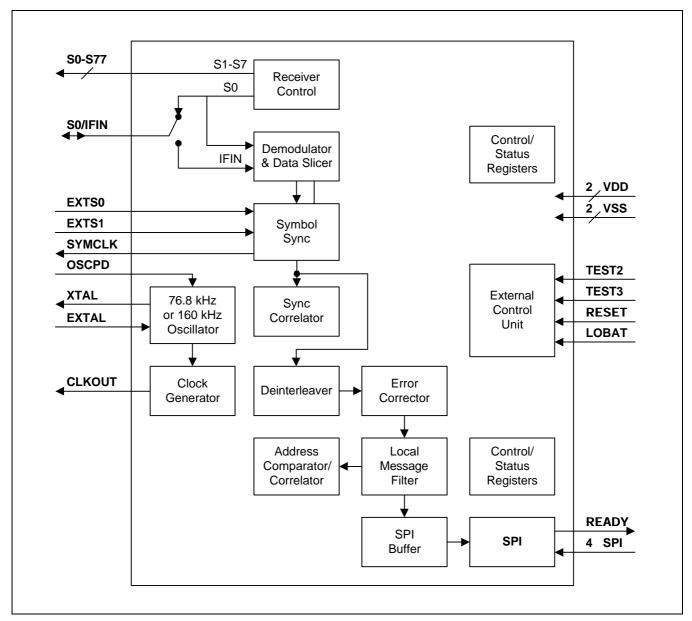

Figure 3 : Block Diagram

## **PIN DESCRIPTION**

| PIN NAME        | PIN                      | TYPE     | DESCRIPTION                                                                                                                                          |  |  |  |

|-----------------|--------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                 |                          |          | Power                                                                                                                                                |  |  |  |

| V <sub>DD</sub> | 3,13                     |          | Power                                                                                                                                                |  |  |  |

| V <sub>SS</sub> | 7,29                     |          | Ground                                                                                                                                               |  |  |  |

| LOBAT           | 10                       |          | Low battery detect input                                                                                                                             |  |  |  |

|                 | Reset                    |          |                                                                                                                                                      |  |  |  |

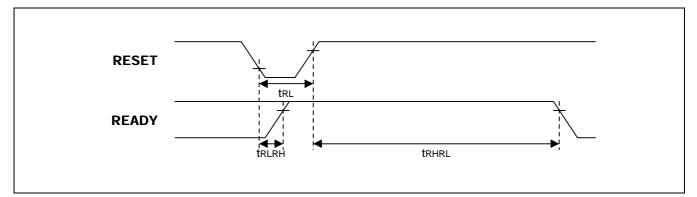

| RESET           | 24                       | I        | Active low reset to the S5T8702.                                                                                                                     |  |  |  |

|                 | -                        | External | Symbol Input Signals                                                                                                                                 |  |  |  |

| EXTS1           | 11                       | I        | MSb of the symbol currently being decoded                                                                                                            |  |  |  |

| EXTS0           | 12                       |          | LSb of the symbol currently being decoded                                                                                                            |  |  |  |

|                 |                          |          | SPI Signals                                                                                                                                          |  |  |  |

| SS              | 27                       | I        | Slave Select for SPI communications                                                                                                                  |  |  |  |

| SCK             | 28                       | I        | Serial Clock for SPI communications                                                                                                                  |  |  |  |

| MOSI            | 30                       | I        | Data input for SPI communications                                                                                                                    |  |  |  |

| MISO            | 31                       | 0        | Three-state data output for SPI communications                                                                                                       |  |  |  |

| READY           | 26                       | 0        | Driven low when the IC is ready for an SPI packet                                                                                                    |  |  |  |

|                 |                          | (        | Clock Signals                                                                                                                                        |  |  |  |

| CLKOUT          | 32                       | 0        | 38.4 kHz or 40kHz clock output(derived from oscillator)                                                                                              |  |  |  |

| SYMCLK          | 14                       | 0        | Recovered symbol clock                                                                                                                               |  |  |  |

| EXTAL           | 6                        | I        | 76.8 kHz or 160kHz crystal input or external input                                                                                                   |  |  |  |

| XTAL            | 5                        | 0        | 76.8 kHz or 160kHz clock output                                                                                                                      |  |  |  |

| OSCPD           | 2                        | Ι        | Internal oscillator power down.<br>Connected to <b>VSS</b> when using internal oscillator.<br>Connected to <b>VDD</b> when using an external source. |  |  |  |

|                 |                          | Rece     | iver Control Lines                                                                                                                                   |  |  |  |

| S1 - S7         | 22,21,20,1<br>9,18,16,15 | 0        | Seven three-state receiver control output                                                                                                            |  |  |  |

| S0 / IFIN       | 23                       | 0/1      | S0 : Receiver control output when using external demodulator<br>IFIN : Limited IF input when using internal demodulator                              |  |  |  |

|                 |                          |          | Test pins                                                                                                                                            |  |  |  |

| TEST2, TEST3    | 4,8                      | Ι        | IC manufacturing test mode pin.<br>Normally connected to <b>VSS</b> .                                                                                |  |  |  |

| NC              | 1,9,17,25                | 0        | IC manufacturing test mode on.<br>Normally connected to Vss. (Can be left unconnected.)                                                              |  |  |  |

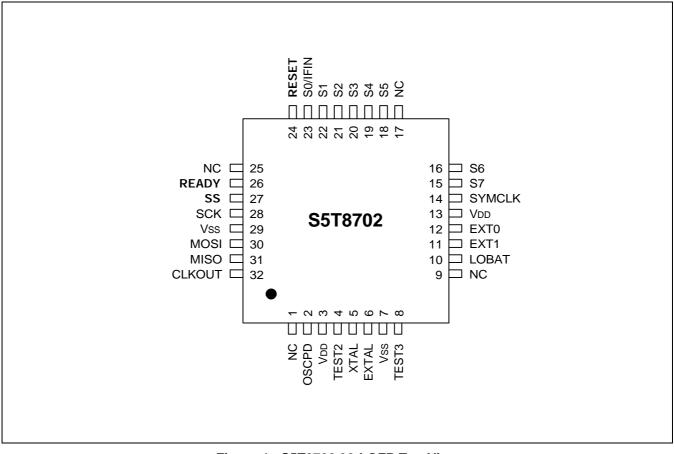

# **PIN CONFIGURATION**

Figure 4 : S5T8702 32-LQFP Top View

# FUNCTIONAL DESCRIPTION

## SPI PACKETS

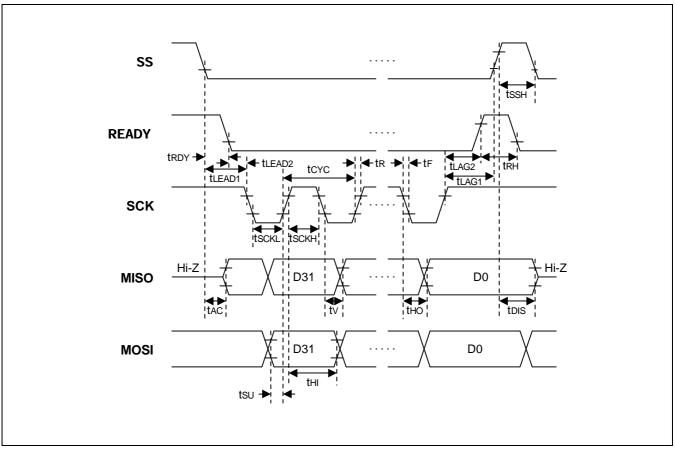

All data communicated between the S5T8702 and the host MCU is transmitted on the SPI in 32-bit packets. Each packet consists of an 8-bit ID followed by 24 bits of information. The S5T8702 uses the SPI bus in full duplex mode. In other words, whenever a packet communication occurs, the data in both directions is valid packet data.

The SPI interface consists of a **READY** pin and four SPI pins (**SS, SCK, MOSI**, and **MISO**). The **SS** is used as a chip select for the S5T8702. The **SCK** is a clock supplied by the host MCU. The data from the host is transmitted on the **MOSI**(Master-Out-Slave-In) line. The data from the S5T8702 is transmitted on the **MISO**(Master-In-Slave-Out) line.

Timing requirements for SPI communication are specified in "SPI Timing" on page 60.

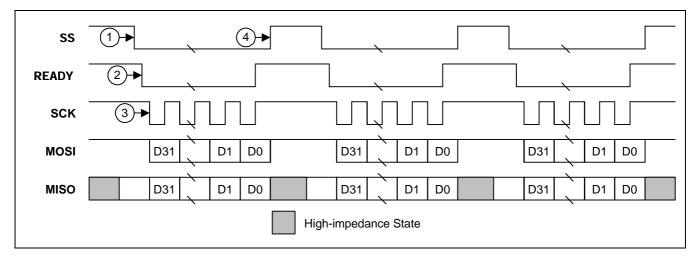

## PACKET COMMUNICATION INITIATED BY THE HOST

Refer to figure 6 on page 10. When the host sends a packet to the S5T8702, it performs the following steps:

- 1. Select the S5T8702 by driving the **SS** pin low.

- 2. Wait for the S5T8702 to drive the **READY** pin low.

- 3. Send the 32-bit packet.

- 4. De-select the S5T8702 by driving the **SS** pin high.

- 5. Repeat steps 1 through 4 for each additional packet.

Figure 6: Typical Multiple Packet Communications Initiated by the Host

When the host sends a packet, it will also receive a valid packet from the S5T8702. If the S5T8702 is enabled (see <u>"Checksum Packet" on page 15</u> for a definition of enabled) and has no other packets waiting to be sent, the S5T8702 will send a status packet.

The host must transition the **SS** pin from high to low to begin each 32-bit packet. The S5T8702 must see a negative transition on the **SS** pin in order for the host to initiate each packet communication.

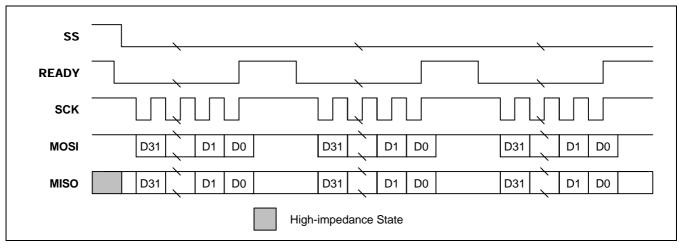

# PACKET COMMUNICATION INITIATED BY THE FLEX DECODER IC

Refer to figure 7 on page 11. When the S5T8702 has a packet for the host to read, the following occurs:

- 1. The S5T8702 drives the **READY** pin low.

- 2. If the S5T8702 is not already selected, the host selects the S5T8702 by driving the **SS** pin low.

- 3. The host receives (and sends) a 32-bit packet.

- 4. The host de-selects the S5T8702 by driving the **SS** pin high (optional).

| SS    |                                                                                               |

|-------|-----------------------------------------------------------------------------------------------|

| READY |                                                                                               |

| SCK   | ₃+」,」」」」」,」」」                                                                                 |

| MOSI  | D31 D1 D0 D31 D1 D0 D31 D1 D0                                                                 |

| MISO  | D31         D1         D0         D31         D1         D0         D31         D1         D0 |

|       | High-impedance State                                                                          |

Figure 7: Typical Multiple Packet Communications Initiated by the FLEX decoder IC

When the host is reading a packet from the S5T8702, it must send a valid packet to the S5T8702. If the host has no data to send, it is suggested that the host send a Checksum Packet with all of the data bits set to 0 in order to avoid disabling the S5T8702. See "Checksum Packet" on page 15 for more details on enabling and disabling the S5T8702.

The following figure illustrates that it is not necessary to de-select the S5T8702 between packets then the packets are initiated by the S5T8702.

Figure 8: Multiple Packet Communications Initiated by the FLEX decoder IC with No De-select

# HOST-TO-DECODER PACKET MAP

The upper 8 bits of a packet comprise the packet ID. The following table describes the packet id's for all of the packets that can be sent to the S5T8702 from the host.

| Packet ID (Hexadecimal) | Packet Type                                           | Page |

|-------------------------|-------------------------------------------------------|------|

| 00                      | Checksum                                              | 16   |

| 02                      | Configuration                                         | 18   |

| 02                      | Control                                               | 21   |

| 03                      | All Frame Mode                                        | 23   |

| 04— 0E                  | Reserved (Host should never send)                     |      |

| 0F                      | Receiver Line Control                                 | 29   |

| 10                      | Receiver Control Configuration (Off setting)          | 30   |

| 11                      | Receiver Control Configuration (Warm Up 1 Setting)    | 31   |

| 12                      | Receiver Control Configuration (Warm Up 2 Setting)    | 31   |

| 13                      | Receiver Control Configuration (Warm Up 3 Setting)    | 31   |

| 14                      | Receiver Control Configuration (Warm Up 4 Setting)    | 31   |

| 15                      | Receiver Control Configuration (Warm Up 5 Setting)    | 31   |

| 16                      | Receiver Control Configuration (3200sps Sync Setting) | 32   |

| 17                      | Receiver Control Configuration (1600sps Sync Setting) | 33   |

| 18                      | Receiver Control Configuration (3200sps Data Setting) | 33   |

| 19                      | Receiver Control Configuration (1600sps Data Setting) | 33   |

| 1A                      | Receiver Control Configuration (Shut Down 1 Setting)  | 34   |

| 1B                      | Receiver Control Configuration (Shut Down 2 Setting)  | 34   |

| 1C— 1F                  | Special (Ignored by S5T8702)                          |      |

| 20                      | Frame-Assignment (Frames 112 through 127)             | 35   |

| 21                      | Frame Assignment (Frames 96 through 111)              | 35   |

| 22                      | Frame Assignment (Frames 80 through 95)               | 35   |

| 23                      | Frame Assignment (Frames 64 through 79)               | 35   |

Table 1: Host-to-Decoder Packet ID Map

| Packet ID (Hexadecimal) | Packet Type                               | Page |

|-------------------------|-------------------------------------------|------|

| 24                      | Frame Assignment (Frames 48 through 63)   | 35   |

| 25                      | Frame Assignment (Frames 32 through 47)   | 35   |

| 26                      | Frame Assignment (Frames 16 through 31)   | 35   |

| 27                      | Frame Assignment (Frames 0 through 15)    | 35   |

| 28 — 77                 | Reserved (Host should never send)         |      |

| 78                      | User Address Enable                       | 36   |

| 79 - 7F                 | Reserved (Host should never send)         |      |

| 80                      | User Address Assignment (User address 0)  | 37   |

| 81                      | User Address Assignment (User address 1)  | 37   |

| 82                      | User Address Assignment (User address 2)  | 37   |

| 83                      | User Address Assignment (User address 3)  | 37   |

| 84                      | User Address Assignment (User address 4)  | 37   |

| 85                      | User Address Assignment (User address 5)  | 37   |

| 86                      | User Address Assignment (User address 6)  | 37   |

| 87                      | User Address Assignment (User address 7)  | 37   |

| 88                      | User Address Assignment (User address 8)  | 37   |

| 89                      | User Address Assignment (User address 9). | 37   |

| 8A                      | User Address Assignment (User address 10) | 37   |

| 8B                      | User Address Assignment (User address 11) | 37   |

| 8C                      | User Address Assignment (User address 12) | 37   |

| 8D                      | User Address Assignment (User address 13) | 37   |

| 8E                      | User Address Assignment (User address 14) | 37   |

| 8F                      | User Address Assignment (User address 15) | 37   |

| 90 - FF                 | Reserved (Host should never send)         |      |

Table 1: Host-to-Decoder Packet ID Map (Continued)

# DECODER-TO-HOST PACKET MAP

The following table describes the packet ID's for all of the packets that can be sent to the host from the S5T8702.

| Packet ID (Hexadecimal) | Packet Type                                    | Page |

|-------------------------|------------------------------------------------|------|

| 00                      | Block Information Word                         | 34   |

| 01                      | Address                                        | 36   |

| 02 — 57                 | Vector or Message (ID is word number in frame) | 37   |

| 58 — 7E                 | Reserved                                       |      |

| 7F                      | Status                                         | 43   |

| 80— FE                  | Reserved                                       |      |

| FF                      | Part ID                                        | 45   |

| Table 2: Decoder-to-Host Packet ID Ma | ар |

|---------------------------------------|----|

|---------------------------------------|----|

# **HOST-TO-DECODER PACKET DESCRIPTIONS**

The following sections describe the packets of information sent from the host to the S5T8702. In all cases the packets should be sent MSB first (bit 7 of byte 3 = bit 31 of the packet = MSB).

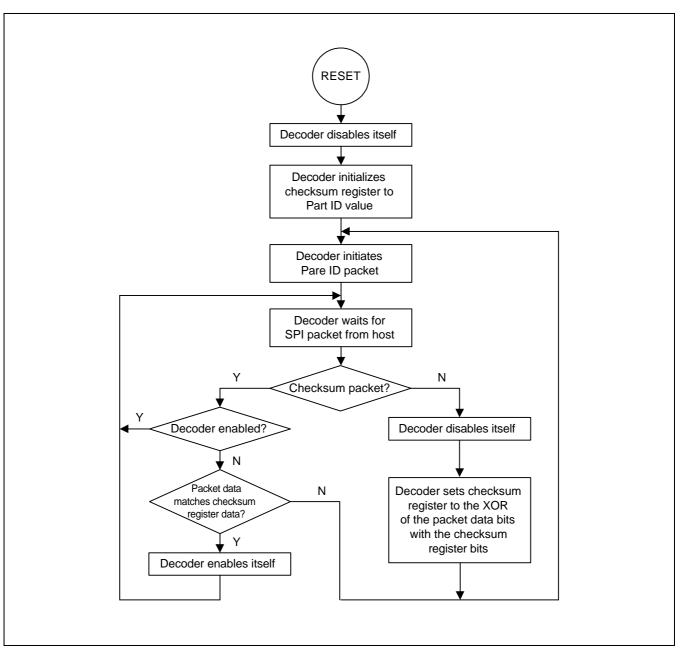

### CHECKSUM PACKET

The Checksum Packet is used to insure proper communication between the host and the S5T8702. The S5T8702 exclusive-or's the 24 data bits of every packet it receives (except the Checksum Packet and the special packet ID's 1C through 1F hexadecimal) with an internal checksum register. Upon reset and whenever the host writes a packet to the S5T8702, the S5T8702 is disabled from sending any information to the host processor until the host processor sends a Checksum Packet with the proper checksum value (**CV**) to the S5T8702. When the S5T8702 is disabled in this way, it prompts the host to read the Part ID Packet. Note that all other operation continues normally when the S5T8702 is "disabled". Disabled only implies that data cannot be read, all other internal operations continue to function.

When the S5T8702 is reset, it is disabled and the internal checksum register is initialized to the 24 bit part ID defined in the Part ID Packet. See <u>"Part ID Packet" on page 46</u> for a description of the Part ID. Every time a packet other than the Checksum Packet and the special packets 1C through 1F is sent to the S5T8702, the value sent in the 24 information bits is exclusive-or'ed with the internal checksum register, the result is stored back to the checksum register, and the S5T8702 is disabled. If a Checksum Packet is sent and the S5T8702 is already enabled, the packet is ignored by the S5T8702 in which case a null packet having the ID and data bits set to 0 is suggested. If a packet other than the Checksum Packet is sent when the S5T8702 will be disabled until a Checksum Packet is sent with the correct **CV** bits.

When the host reads a packet out of the S5T8702 but has no data to send, the Checksum Packet should be sent so the S5T8702 will not be disabled. The data in the Checksum Packet could be a null packet (32 bit stream of all zeros) since a Checksum Packet will not disable the S5T8702. When the host re-configures the S5T8702, the S5T8702 will be disabled from sending any packets other than the Part ID Packet until the S5T8702 is enabled with a Checksum Packet having the proper data. The ID of the Checksum Packet is 0.

|        | Bit 7            | Bit 6            | Bit 5            | Bit 4            | Bit 3            | Bit 2            | Bit 1            | Bit 0            |

|--------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| Byte 3 | 0                | 0                | 0                | 0                | 0                | 0.               | 0                | 0                |

| Byte 2 | CV <sub>23</sub> | CV <sub>22</sub> | CV <sub>21</sub> | CV <sub>20</sub> | CV <sub>19</sub> | CV <sub>18</sub> | CV <sub>17</sub> | CV <sub>16</sub> |

| Byte 1 | CV <sub>15</sub> | $CV_{14}$        | CV <sub>13</sub> | CV <sub>12</sub> | CV <sub>11</sub> | CV <sub>10</sub> | CV <sub>9</sub>  | CV <sub>8</sub>  |

| Byte 0 | CV <sub>7</sub>  | CV <sub>6</sub>  | CV <sub>5</sub>  | $CV_4$           | CV <sub>3</sub>  | CV <sub>2</sub>  | CV <sub>1</sub>  | CV <sub>0</sub>  |

### Table 3: Checksum Packet Bit Assignments

CV: Checksum Value.

Figure 9: FLEX Decoder IC Checksum Flow Chart

### **CONFIGURATION PACKET**

The Configuration Packet defines a number of different configuration options for the S5T8702. Proper operation is not guaranteed if these settings are changed when decoding is enabled (i.e. the **ON** bit in the Control Packet is set). The ID of the Configuration Packet is 1.

|        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1            | Bit 0           |

|--------|-------|-------|-------|-------|-------|-------|------------------|-----------------|

| Byte 3 | 0     | 0     | 0     | 0     | 0     | 0     | 0                | 1               |

| Byte 2 | 0     | DFC   | 0     | 0     | 0     | IDE   | OFD <sub>1</sub> | $OFD_0$         |

| Byte 1 | 0     | 0     | 0     | 0     | 0     | PCE   | SP <sub>1</sub>  | SP <sub>0</sub> |

| Byte 0 | SME   | MOT   | COD   | MTE   | LBP   | ICO   | 0                | 0               |

**Table 4: Configuration Packet Bit Assignments**

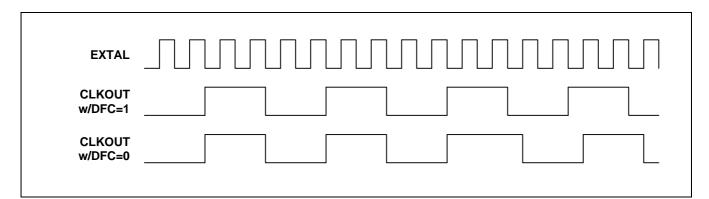

**DFC:** Disable Fractional Clock. When this bit is set and IDE is set, the CLKOUT signal will generate a 40kHz signal (EXTAL divided by 4). When this bit is cleared and IDE is set, the CLKOUT signal will generate 38.4kHz signal (EXTAL fractionally divided by 25/6 see diagram below). This bit has no effect when IDE is cleared. (value after reset=0)

IDE: Internal Demodulator Enable. When this bit is set, the internal demodulator is enabled and clock frequency at **EXTAL** is expected to be 160kHz. When this bit is cleared, the internal demodulator is disabled and the clock frequency at **EXTAL** is expected to be 76.8kHz. (value after reset=0)

OFD: Oscillator Frequency Difference. These bits describe the maximum difference in the frequency of the 76.8kHz oscillator crystal with respect to the frequency of the transmitter. These limits should be the worst case difference in frequency due to all conditions including but not limited to aging, temperature, and manufacturing tolerance. Using a smaller frequency difference in this packet will result in lower power consumption due to higher receiver battery save ratios. Note that this value is not the absolute error of the oscillator frequency provided to the S5T8702. The absolute error of the clock used by the FLEX transmitter must be taken into account. (e.g. If the transmitter tolerance is ± 25ppm and the 76.8kHz oscillator tolerance is +/-140ppm, the oscillator frequency difference is ± 165ppm and OFD should be set to 0.)(value after reset=0)

| OFD1 | OFD <sub>0</sub> | Frequency Difference |

|------|------------------|----------------------|

| 0    | 0                | $\pm$ 300ppm         |

| 0    | 1                | ± 150ppm             |

| 1    | 0                | ± 75ppm              |

| 1    | 1                | ± 0ppm               |

- PCE: Partial Correlation Enable. When this bit is set, partial correlation of addresses is enabled. When partial correlation is enabled, the S5T8702 will shutdown the receiver before the end of the last FLEX block which contains addresses if it can determine that none of the addresses in that FLEX block will match any enabled address in the S5T8702. When this bit is cleared, the receiver will be controlled as it was in previous versions of the IC.(value after reset=0)

- **SP:** Signal Polarity. These bits set the polarity of **EXTS1** and **EXTS0** input signals. (value after reset=0) The polarity of the **EXTS0** and **EXTS1** bits will be determined by the receiver design.

| SP1 | SP0 | Signal Polarity EXTS1 EXTS0 |          |  |  |

|-----|-----|-----------------------------|----------|--|--|

| 0   | 0   | Normal                      | Normal   |  |  |

| 0   | 1   | Normal                      | Inverted |  |  |

| 1   | 0   | Inverted                    | Normal   |  |  |

| 1   | 1   | Inverted                    | Inverted |  |  |

| FSK Modulation<br>@SP = 0, 0 | EXTS1 | EXTS0 |

|------------------------------|-------|-------|

| +4800Hz                      | 1     | 0     |

| +1600Hz                      | 1     | 1     |

| -1600Hz                      | 0     | 1     |

| -4800Hz                      | 0     | 0     |

- SME: Synchronous Mode Enable. When this bit is set, a Status Packet will be automatically sent whenever the SMU (synchronous mode update) bit in the Status Packet is set. The host can use the SM (synchronous mode) bit in the Status Packet as an in-range/out-of-range indication. (value after reset=0)

- MOT: Maximum Off Time. This bit has no effect if **AST** in the Timing Control Packet is non-zero. When **AST**=0 and **MOT**=0, asynchronous A-word searches will time-out in 4 minutes. When **AST**=0 and **MOT**=1, asynchronous A-word searches will time-out in 1 minute. (value after reset=0)

- COD: Clock Output Disable. When this bit is clear, a 38.4kHz or 40kHz(depending on IDE and DFC) signal will be output on the CLKOUT pin. When this bit is set, the CLKOUT pin will be driven low. Note that setting and clearing this bit can cause pulses on the CLKOUT pin that are less than one half the clock period. Also note that when the clock output is enabled and not set for clock intermittent operation(see ICO in this packet), the CLKOUT pin will always output the clock signal even when the S5T8702 is in reset (as long as the S5T8702 oscillator is seeing clocks). Further note that the when the S5T8702 is used in internal demodulator mode(i.e. uses a 160kHz oscillator), the CLKOUT pin will be 80kHz from reset until the time the IDE bit is set. This is because the S5T8702 defaults to external demodulator mode at reset. (value after reset=0)

- MTE: Minute Timer Enable. When this bit is set, a Status Packet will be sent at one minute intervals with the **MT** (minute time-out) bit in the Status Packet set. When this bit is clear, the internal one-minute timer stops counting. The internal one-minute timer is reset when this bit is changed from 0 to 1 or when the **MTC** (minute timer clear) bit in the Control Packet is set. Note that the minute timer will not be accurate using a 160kHz oscillator until the **IDE** bit is set. (value after reset=0)

- LBP: Low Battery Polarity. This bit defines the polarity of the S5T8702's LOBAT pin. The LB bit in the Status Packet is initialized to the inverse value of this bit when the S5T8702 is turned on (by setting the ON bit in the Control Packet). When the S5T8702 is turned on, the first low battery update in the Status Packet will be sent to the host when a low battery condition is detected on the LOBAT pin. Setting this bit means that a high on the LOBAT pin indicates a low voltage condition. (value after reset=0)

- ICO: Intermittent Clock Out. When this bit is clear and COD is clear, a 38.4kHz or 40kHz (depending on the values of IDE and DFC) signal will be output on the CLKOUT pin. When this bit is set and COD is clear, the clock will only be output on the CLKOUT pin while the receiver is not in the Off state. The clock will be output for a few cycles before the receiver transitions from the off state and for a few cycles after the receiver transitions to the off state (this is to insure that the receiver receives enough clocks to detect and process the changes to and from the Off state). The CLKOUT pin will be driven low when it is not driving a clock. Note that when the clock is automatically enabled and disabled (i.e. when ICO is set), the CLKOUT signal transitions will be clean (i.e. no pulses less than half the clock period) when it transitions between no clock and clocked output. This bit has no effect when COD is set. (value after reset=0)

# CONTROL PACKET

The Control Packet defines a number of different control bits for the S5T8702. The ID of the Control Packet is 2.

|        | Bit 7           | Bit 6  | Bit 5 | Bit 4           | Bit 3  | Bit 2  | Bit 1           | Bit 0  |

|--------|-----------------|--------|-------|-----------------|--------|--------|-----------------|--------|

| Byte 3 | 0               | 0      | 0     | 0               | 0      | 0      | 1               | 0      |

| Byte 2 | FF <sub>7</sub> | $FF_6$ | FF₅   | $FF_4$          | $FF_3$ | $FF_2$ | FF <sub>1</sub> | $FF_0$ |

| Byte 1 | 0               | SPM    | PS₁   | PS <sub>0</sub> | 0      | 0      | 0               | 0      |

| Byte 0 | 0               | SBI    | 0     | MTC             | 0      | 0      | EAE             | ON     |

#### **Table 5: Control Packet Bit Assignments**

- FF: Force Frame 0-7. These bits enable and disable forcing the S5T8702 to look in frames 0 through 7. When an **FF** bit is set, the S5T8702 will decode the corresponding frame. Unlike the **AF** bits in the Frame Assignment Packets, the system collapse of a FLEX system will not affect frames assigned using the **FF** bits (e.g. Where as setting **AF**<sub>0</sub> to 1 when the system collapse is 5 will cause the S5T8702 to decode frames 0, 32, 64, and 96, setting **FF**<sub>0</sub> to 1 when the system collapse is 5 will only cause the S5T8702 to decode frame 0.). This may be useful for acquiring transmitted time information or channel attributes (e.g. Local ID). (value after reset =0)

- **SPM:** Single Phase Mode. When this bit is set, the S5T8702 will decode only one phase of the transmitted data. When this bit is clear, the S5T8702 will decode all of the phases it receives. A change to this bit while the S5T8702 is on, will not take affect until the next block 0 of the next decoded frame. (value after reset =0)

- **PS:** Phase Select. When the **SPM** bit is set, these bits define what phase the S5T8702 should decode according to the following table. This value is determined by the service provider. A change to these bits while the S5T8702 is on, will not take affect until the next block 0 of a frame. (value after reset =0)

| PS V | /alue | Phase Decoded (based on FLEX Data Rate) |         |         |  |  |  |

|------|-------|-----------------------------------------|---------|---------|--|--|--|

| PS1  | PS0   | 1600bps                                 | 3200bps | 6400bps |  |  |  |

| 0    | 0     | а                                       | а       | а       |  |  |  |

| 0    | 1     | а                                       | а       | b       |  |  |  |

| 1    | 0     | а                                       | С       | С       |  |  |  |

- **SBI:** Send Block Information words 2-4. When this bit is set, any errored or time related block information words 2-4 will be sent to the host. See <u>"Block Information Word Packet" on page34</u> for a description of the words sent. (value after reset=0)

- MTC: Minute Timer Clear. Setting this bit will cause the one minute timer to restart from 0.

- **EAE:** End of Addresses Enable. When this bit is set, the **EA** bit in the Status Packet will be set immediately after the S5T8702 decodes the last address word in the frame if there was any address detected in the frame. When this bit is cleared, the **EA** bit will never be set.

- **ON:** Turn On Decoder. Set if the S5T8702 should be decoding FLEX signals. Clear if signal processing should be off (very low power mode). If the **ON** bit is changed twice and the control packets making the changes are received within 2ms of each other, the S5T8702 may ignore the double change and stay in its original state (e.g. if it is turned off then on again within 2ms it may stay on and ignore the off pulse). Therefore it is recommended that the host insures a minimum of 2ms between changes in the **ON** bit. (value after reset=0)

- **NOTES:** Turning off the S5T8702 must be done using the following sequence. This sequence is performed automatically by the FLEX stack software version 1.2 and greater.

- 1. Turn off the S5T8702 by sending a Control Packet with the **ON** bit cleared.

- 2. Turn on the S5T8702 by sending a Control Packet with the **ON** bit set.

- 3. Turn off the S5T8702 by sending a Control Packet with the **ON** bit cleared.

Timing between these steps is specified below and is measured from the positive edge of the last clock of one packet to the positive edge of the last clock of the next packet:

- The minimum time between steps 1 and 2 is 2ms or the programmed shut down time, whichever is greater. The programmed shut down time is the sum of all the of the times. programmed in the used Receiver Shut Down Settings Packets.

- There is no maximum time between steps 1 and 2.

- The minimum time between steps 2 and 3 is 2ms.

- The maximum time between steps 2 and 3 is the programmed warm up time minus 2ms. The programmed warm up time is the sum of all the of the times programmed in the used Receiver Warm Up Settings Packets.

# ALL FRAME MODE PACKET

The All Frame Mode Packet is used to decrement temporary address enable counters by one, decrement the all frame mode counter by one, and/or enable or disable forcing all frame mode. All frame mode is enabled if any temporary address enable counter is non-zero, the all frame mode counter is non-zero, or the force all frame mode bit is set. If all frame mode is enabled, the S5T8702 will attempt to decode every frame and send a Status Packet with the EOF (end-of-frame) bit set at the end of every frame. Both the all frame mode counter and the temporary address enable counters can only be incremented internally by the S5T8702 and can only be decremented by the host. The S5T8702 will increment a temporary address enable counter whenever a short instruction vector is received assigning the corresponding temporary address. See "Operation of a Temporary Address" on page 64 for details. The S5T8702 will increment the all frame mode counter whenever an alphanumeric. HEX / binary, or secure vector is received. When the host determines that a message associated with a temporary address, or a fragmented message has ended, then the appropriate temporary address counter or all frame mode counter should be decremented by writing an All Frame Mode Packet to the S5T8702 in order to exit the all frame mode, thereby improving battery life. See "Building a Fragmented Message" on page 54 for details. Neither the temporary address enable counters nor the all frame mode counter can be incremented past the value 127 (i.e. it will not roll-over) or decremented past the value 0. The temporary address enable counters and the all frame mode counter are initialized to 0 at reset and when the decoder is turned off. The ID of the All Frame Mode Packet is 3.

|        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0            |

|--------|-------|-------|-------|-------|-------|-------|-------|------------------|

| Byte 3 | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1                |

| Byte 2 | DAF   | FAF   | 0     | 0     | 0     | 0     | 0     | 0                |

| Byte 1 | DTA15 | DTA14 | DTA13 | DTA12 | DTA11 | DTA10 | DTA9  | DTA8             |

| Byte 0 | DTA7  | DTA6  | DTA5  | DTA4  | DTA3  | DTA2  | DTA1  | DTA <sub>0</sub> |

- **DAF:** Decrement All Frame counter. Setting this bit decrements the all frame mode counter by one. If a packet is sent with this bit clear, the all frame mode counter is not affected. (value after reset=0)

- **FAF:** Force All Frame mode. Setting this bit forces the S5T8702 to enter all frame mode. If this bit is clear, the S5T8702 may or may not be in all frame mode depending on the status of the all frame mode counter and the temporary address enable counters. This may be useful in acquiring transmitted time information.(value after reset=0)

- **DTA:** Decrement Temporary Address enable counter. When a bit in this word is set, the corresponding temporary address enable counter is decremented by one. When a bit is cleared, the corresponding temporary address enable counter is not affected. When a temporary address enable counter reaches zero, the temporary address is disabled.(value after reset=0)

The operator messaging address enable packet is used to enable and disable the built-in FLEX operator messaging addresses. Enabling and disabling operator messaging addresses does not affect what frames the decoder IC decodes. To decode the proper frames, the host must modify the FF bits in the Control Packet or the AF bits in the Frame Assignment Packets. The ID of the operator messaging address enable packet is 4.

|        | Bit 7             | Bit 6             | Bit 5             | Bit 4             | Bit 3             | Bit 2             | Bit 1            | Bit 0            |

|--------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Byte 3 | 0                 | 0                 | 0                 | 0                 | 0                 | 1                 | 0                | 0                |

| Byte 2 | 0                 | 0                 | 0                 | 0                 | 0                 | 0                 | 0                | 0                |

| Byte 1 | OAE <sub>15</sub> | OAE <sub>14</sub> | OAE <sub>13</sub> | OAE <sub>12</sub> | OAE <sub>11</sub> | OAE <sub>10</sub> | OAE <sub>9</sub> | OAE <sub>8</sub> |

| Byte 0 | OAE <sub>7</sub>  | OAE <sub>6</sub>  | OAE <sub>5</sub>  | OAE <sub>4</sub>  | $OAE_3$           | OAE <sub>2</sub>  | OAE <sub>1</sub> | OAE <sub>0</sub> |

### Table 7: System Address Enable Packet Bit Assignments

OAE: Operator messaging Address Enable. When a bit is set, the corresponding operator messaging address is enabled. When it is cleared, the corresponding operator messaging address is disabled. OAE<sub>0</sub> through OAE<sub>15</sub> corresponds to the hexadecimal operator messaging address values of 1F7810 through 1F781F respectively. (value after reset=0)

# **RECEIVER LINE CONTROL PACKET**

This packet gives the host control over the settings on the receiver control lines (**S0-S7**) in all modes except reset. In reset, the receiver control lines are in high impedance settings. The ID for the Receiver Line Control Packet is 15 (decimal).

|        | Bit 7            | Bit 6            | Bit 5   | Bit 4   | Bit 3            | Bit 2            | Bit 1            | Bit 0            |

|--------|------------------|------------------|---------|---------|------------------|------------------|------------------|------------------|

| Byte 3 | 0                | 0                | 0       | 0       | 1                | 1                | 1                | 1                |

| Byte 2 | 0                | 0                | 0       | 0       | 0                | 0                | 0                | 0                |

| Byte 1 | FRS <sub>7</sub> | $FRS_6$          | FRS₅    | $FRS_4$ | FRS₃             | $FRS_2$          | FRS₁             | FRS₀             |

| Byte 0 | CLS <sub>7</sub> | CLS <sub>6</sub> | $CLS_5$ | $CLS_4$ | CLS <sub>3</sub> | CLS <sub>2</sub> | CLS <sub>1</sub> | CLS <sub>0</sub> |

- FRS: Force Receiver Setting. Setting a bit to one will cause the corresponding CLS bit in this packet to override the internal receiver control settings on the corresponding receiver control line (S0 S7). Clearing a bit gives control of the corresponding receiver control lines (S0 S7) back to the S5T8702. (value after reset=0)

- **CLS:** Control Line Setting. If the corresponding **FRS** bit was set in this packet, these bits define what setting should be applied to the corresponding receiver control lines.(value after reset=0)

## **RECEIVER CONTROL CONFIGURATION PACKETS**

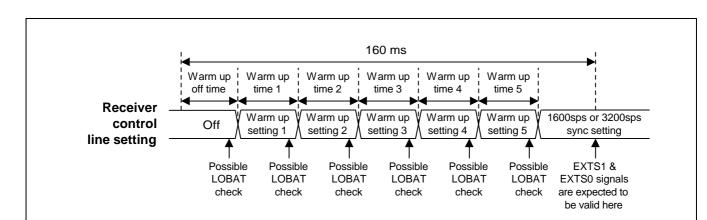

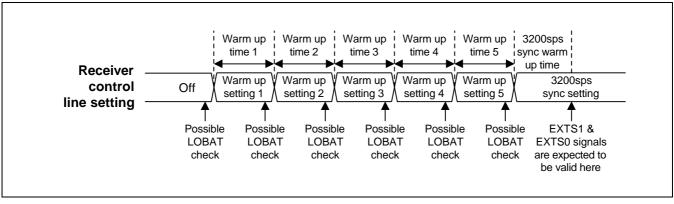

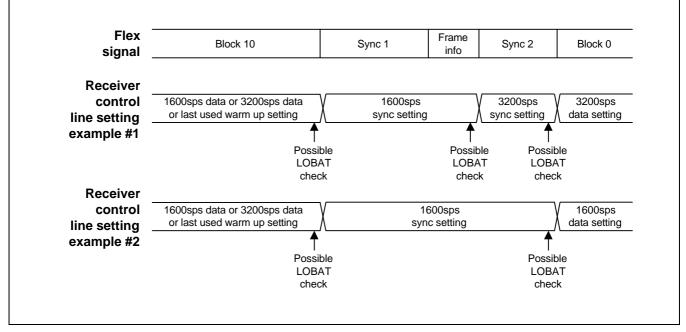

These packets allow the host to configure what setting is applied to the receiver control lines **SO-S7**, how long to apply the setting, and when to read the value of the **LOBAT** input pin. For a more detailed description of how the S5T8702 uses these settings see <u>"Receiver Control" on page 48</u>. The S5T8702 defines 12 different receiver control settings. Proper operation is not guaranteed if these settings are changed when decoding is enabled (i.e. the **ON** bit in the Control Packet is set). The IDs for these packets range from 16 to 27 (decimal).

#### **Receiver Off setting Packet**

|        | Bit 7            | Bit 6            | Bit 5            | Bit 4   | Bit 3            | Bit 2            | Bit 1            | Bit 0            |

|--------|------------------|------------------|------------------|---------|------------------|------------------|------------------|------------------|

| Byte 3 | 0                | 0                | 0                | 1       | 0                | 0                | 0                | 0                |

| Byte 2 | 0                | 0                | 0                | 0       | LBC              | 0                | 0                | 0                |

| Byte 1 | CLS <sub>7</sub> | CLS <sub>6</sub> | CLS <sub>5</sub> | $CLS_4$ | CLS <sub>3</sub> | CLS <sub>2</sub> | CLS <sub>1</sub> | CLS <sub>0</sub> |

| Byte 0 | ST <sub>7</sub>  | ST <sub>6</sub>  | ST₅              | $ST_4$  | ST <sub>3</sub>  | ST <sub>2</sub>  | ST₁              | ST <sub>0</sub>  |

#### **Table 11: Receiver Off setting Packet Bit Assignments**

- **LBC:** Low Battery Check. If this bit is set, the S5T8702 will check the status of the **LOBAT** port just before leaving this receiver state. (value after reset=0)

- **CLS:** Control Line Setting. This is the value to be output on the receiver control lines (**S0 S7**) for this receiver state. (value after reset=0)

- **ST:** Step Time. This is the time the S5T8702 is to keep the receiver off before applying the first warm up state's receiver control value to the receiver control lines. The setting is in steps of 625us. Valid values are 625us (**ST**=01) to 159.375ms (**ST**=FF in hexadecimal). (value after reset=625us)

S:

|        | Bit 7            | Bit 6            | Bit 5            | Bit 4           | Bit 3            | Bit 2                 | Bit 1            | Bit 0            |

|--------|------------------|------------------|------------------|-----------------|------------------|-----------------------|------------------|------------------|

| Byte 3 | 0                | 0                | 0                | 1               | 0                | <b>S</b> <sub>2</sub> | S <sub>1</sub>   | <b>S</b> 0       |

| Byte 2 | SE               | 0                | 0                | 0               | LBC              | 0                     | 0                | 0                |

| Byte 1 | CLS <sub>7</sub> | CLS <sub>6</sub> | CLS <sub>5</sub> | $CLS_4$         | CLS <sub>3</sub> | CLS <sub>2</sub>      | CLS <sub>1</sub> | CLS <sub>0</sub> |

| Byte 0 | 0                | $ST_6$           | ST₅              | ST <sub>4</sub> | ST₃              | ST <sub>2</sub>       | ST <sub>1</sub>  | ST <sub>0</sub>  |

Table 12: Receiver Warm Up Setting Packet Bit Assignments

## **RECEIVER WARM UP SETTING PACKETS**

Setting Number. Receiver control setting for which this packet's values are to be applied. The following truth table shows the names of each of the values for s that apply to this packet.

| S <sub>2</sub> S <sub>1</sub> S <sub>0</sub> | Setting Name |

|----------------------------------------------|--------------|

| 001                                          | Warm Up 1    |

| 010                                          | Warm Up 2    |

| 011                                          | Warm Up 3    |

| 100                                          | Warm Up 4    |

| 101                                          | Warm Up 5    |

- **SE:** Step Enable. The receiver setting is enabled when the bit is set. If a step in the warm up sequence is disabled, the disabled step and all remaining steps will be skipped. (value after reset=0)

- **LBC:** Low Battery Check. If this bit is set, the S5T8702 will check the status of the **LOBAT** port just before leaving this receiver state. (value after reset=0)

- **CLS:** Control Line Setting. This is the value to be output on the receiver control lines (**S0 S7**) for this receiver state. (value after reset=0)

- ST: Step Time. This is the time the S5T8702 is to wait before applying the next state's receiver control value to the receiver control lines. The setting is in steps of 625us. Valid values are 625us (ST=01) to 79.375ms (ST=7F in hexadecimal), (value after reset=625us)

## 3200SPS SYNC SETTING PACKETS

|        | Bit 7            | Bit 6            | Bit 5            | Bit 4            | Bit 3            | Bit 2            | Bit 1            | Bit 0            |

|--------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| Byte 3 | 0                | 0                | 0                | 1                | 0                | 1                | 1                | 0                |

| Byte 2 | 0                | 0                | 0                | 0                | LBC              | 0                | 0                | 0                |

| Byte 1 | CLS <sub>7</sub> | CLS <sub>6</sub> | CLS <sub>5</sub> | CLS <sub>4</sub> | CLS <sub>3</sub> | CLS <sub>2</sub> | CLS <sub>1</sub> | CLS <sub>0</sub> |

| Byte 0 | 0                | ST <sub>6</sub>  | ST₅              | ST <sub>4</sub>  | ST <sub>3</sub>  | ST <sub>2</sub>  | ST <sub>1</sub>  | ST <sub>0</sub>  |

#### Table 13: 3200sps Sync Setting Packet Bit Assignments

**LBC:** Low Battery Check. If this bit is set, the S5T8702 will check the status of the **LOBAT** port just before leaving this receiver state. (value after reset=0)

Step Time. This is the time the S5T8702 is to wait before expecting good signals on the EXTS1 and EXTS0 signals after warming up. The setting is in steps of 625us. Valid values are 625us (ST=01) to 79.375ms (ST=7F in hexadecimal). (value after reset=625us)

**CLS:** Control Line Setting. This is the value to be output on the receiver control lines (**SO - S7**) for this receiver state. (value after reset=0)

s:

## **RECEIVER ON SETTING PACKETS**

|        | Bit 7            | Bit 6            | Bit 5            | Bit 4            | Bit 3                 | Bit 2            | Bit 1            | Bit 0            |

|--------|------------------|------------------|------------------|------------------|-----------------------|------------------|------------------|------------------|

| Byte 3 | 0                | 0                | 0                | 1                | <b>S</b> <sub>3</sub> | S <sub>2</sub>   | S <sub>1</sub>   | S <sub>0</sub>   |

| Byte 2 | 0                | 0                | 0                | 0                | LBC                   | 0                | 0                | 0                |

| Byte 1 | CLS <sub>7</sub> | CLS <sub>6</sub> | CLS <sub>5</sub> | CLS <sub>4</sub> | CLS <sub>3</sub>      | CLS <sub>2</sub> | CLS <sub>1</sub> | CLS <sub>0</sub> |

| Byte 0 | 0                | 0                | 0                | 0                | 0                     | 0                | 0                | 0                |

# Table 14: Receiver On Setting Packet Bit Assignments

Setting Number. Receiver control setting for which this packet's values are to be applied. The following truth table shows the names of each of the values for s that apply to this packet.

| S <sub>3</sub> S <sub>2</sub> S <sub>1</sub> S <sub>0</sub> | Setting Name |

|-------------------------------------------------------------|--------------|

| 0 1 1 1                                                     | 1600sps Sync |

| 1000                                                        | 3200sps Data |

| 1001                                                        | 1600sps Data |

- **LBC:** Low Battery Check. If this bit is set, the S5T8702 will check the status of the **LOBAT** port just before leaving this receiver state. (value after reset=0)

- **CLS:** Control Line Setting. This is the value to be output on the receiver control lines (**S0 S7**) for this receiver state. (value after reset=0)

s:

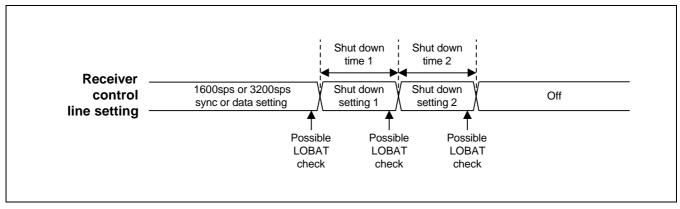

## **RECEIVER SHUT DOWN SETTING PACKETS**

|        | Bit 7            | Bit 6            | Bit 5 | Bit 4           | Bit 3 | Bit 2            | Bit 1            | Bit 0            |

|--------|------------------|------------------|-------|-----------------|-------|------------------|------------------|------------------|

| Byte 3 | 0                | 0                | 0     | 1               | 1     | 0                | 1                | S                |

| Byte 2 | SE               | 0                | 0     | 0               | LBC   | 0                | 0                | 0                |

| Byte 1 | CLS <sub>7</sub> | CLS <sub>6</sub> | CLS₅  | $CLS_4$         | CLS₃  | CLS <sub>2</sub> | CLS <sub>1</sub> | CLS <sub>0</sub> |

| Byte 0 | 0                | 0                | ST₅   | ST <sub>4</sub> | ST₃   | ST <sub>2</sub>  | ST <sub>1</sub>  | ST <sub>0</sub>  |

#### Table 15: Receiver Shut Down Setting Packet Bit Assignments

Setting Number. Receiver control setting for which this packet's values are to be applied. The following truth table shows the names of each of the values for s that apply to this packet.

| S | Setting Name |

|---|--------------|

| 0 | Shut Down 1  |

| 1 | Shut Down 2  |

- SE: Step Enable. The receiver setting is enabled when the bit is set. If a step in the shut down sequence is disabled, all steps following the disabled step will be ignored. (value after reset=0)

- **LBC:** Low Battery Check. If this bit is set, the S5T8702 will check the status of the **LOBAT** port just before leaving this receiver state. (value after reset=0)

- **CLS:** Control Line Setting. This is the value to be output on the receiver control lines (**S0 S7**) for this receiver state. (value after reset=0)

- **ST:** Step Time. This is the time the S5T8702 is to wait before applying the next state's receiver control value to the receiver control lines. The setting is in steps of 625us. Valid values are 625us (**ST**=01) to 39.375ms (**ST**=3F in hexadecimal).(value after reset=625us)

## FRAME ASSIGNMENT PACKETS

The FLEX protocol defines that each address of a FLEX pager is assigned a home frame and a battery cycle. The S5T8702 must be configured so that a frame that is assigned by one or more of the addresses home frames and battery cycles has its corresponding configuration bit set. For example, if the S5T8702 has one enabled address and it is assigned to frame 3 with a battery cycle of 4, the AF bits for frames 3, 19, 35, 51, 67, 83, 99, and 115 should be set and the AF bits for all other frames should be cleared.

When the S5T8702 is configured for manual collapse mode by setting the MCM bit in the Roaming Control Packet, the S5T8702 will not apply the received system collapse to the AF bits. The host should set the AF bits for all frames that should be decoded on all channels. For example, if frames 0 and 64 should be decoded on one channel and frames 4, 36, 68, and 100 should be decoded on another channel, all six of the corresponding AF bits should be set. The host can then change the receiver's carrier frequency after the S5T8702 decodes frames 0, 36, 64, and 100.

There are 8 Frame Assignment Packets. The Packet IDs for these packets range from 32 to 39 (decimal).

|        | Bit 7            | Bit 6            | Bit 5            | Bit 4            | Bit 3            | Bit 2           | Bit 1           | Bit 0           |

|--------|------------------|------------------|------------------|------------------|------------------|-----------------|-----------------|-----------------|

| Byte 3 | 0                | 0                | 1                | 0                | 0                | f <sub>2</sub>  | f <sub>1</sub>  | f <sub>0</sub>  |

| Byte 2 | 0                | 0                | 0                | 0                | 0                | 0               | 0               | 0               |

| Byte 1 | AF <sub>15</sub> | AF <sub>14</sub> | AF <sub>13</sub> | AF <sub>12</sub> | AF <sub>11</sub> | $AF_{10}$       | AF <sub>9</sub> | AF <sub>8</sub> |

| Byte 0 | AF <sub>7</sub>  | AF <sub>6</sub>  | AF <sub>5</sub>  | $AF_4$           | AF <sub>3</sub>  | AF <sub>2</sub> | AF <sub>1</sub> | AF <sub>0</sub> |

#### **Table 16: Frame Assignment Packet Bit Assignments**

f:

Frame range. This value determines which 16 frames correspond to the 16 AF bits in the packet according to the following table. At least one of these bits must be set when the S5T8702 is turned on by setting the ON bit in the control packet. (value after reset=0)

| $f_2 f_1 f_0$ | AF <sub>15</sub> | AF <sub>0</sub> |  |  |  |

|---------------|------------------|-----------------|--|--|--|

| 0 0 0         | Frame 127        | Frame 112       |  |  |  |

| 001           | Frame 111        | Frame 96        |  |  |  |

| 010           | Frame 95         | Frame 80        |  |  |  |

| 011           | Frame 79         | Frame 64        |  |  |  |

| 100           | Frame 63         | Frame 48        |  |  |  |

| 101           | Frame 47         | Frame 32        |  |  |  |

| 1 1 0         | Frame 31         | Frame 16        |  |  |  |

| 1 1 1         | Frame 15         | Frame 0         |  |  |  |

**AF:** Assigned Frame. If a bit is set, the S5T8702 will consider the corresponding frame to be assigned via an address's home frame and pager collapse. (value after reset=0)

## USER ADDRESS ENABLE PACKET

The User Address Enable Packet is used to enable and disable the 16 user address words. Although the host is allowed to change the user address words while the S5T8702 is decoding FLEX signals, the host must disable a user address word before changing it. The ID of the User Address Enable Packet is 120 (decimal).

|        | Bit 7             | Bit 6             | Bit 5             | Bit 4             | Bit 3             | Bit 2             | Bit 1            | Bit 0            |

|--------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Byte 3 | 0                 | 1                 | 1                 | 1                 | 1                 | 0                 | 0                | 0                |

| Byte 2 | 0                 | 0                 | 0                 | 0                 | 0                 | 0                 | 0                | 0                |

| Byte 1 | UAE <sub>15</sub> | UAE <sub>14</sub> | UAE <sub>13</sub> | UAE <sub>12</sub> | UAE <sub>11</sub> | UAE <sub>10</sub> | UAE <sub>9</sub> | UAE <sub>8</sub> |

| Byte 0 | UAE7              | UAE <sub>6</sub>  | $UAE_5$           | $UAE_4$           | UAE <sub>3</sub>  | UAE <sub>2</sub>  | UAE₁             | UAE <sub>0</sub> |

#### Table 17: User Address Enable Packet Bit Assignments

**UAE:** User Address Enable. When a bit is set, the corresponding user address word is enabled. When it is cleared, the corresponding user address word is disabled. **UAE**<sub>0</sub> corresponds to the user address word configured using a packet ID of 128, and **UAE**<sub>15</sub> corresponds to the user address word configured using a packet ID of 143. (value after reset=0)

## USER ADDRESS ASSIGNMENT PACKETS

The S5T8702 has 16 user address words. Each word can be programmed to be a short address, part of a long address, or the first part of a network ID. The addresses are configured using the Address Assignment Packets. Each user address can be configured as long or short and tone-only or regular (network ID's are short and regular). Although the host is allowed to send these packets while the S5T8702 is on, the host must disable the user address word by clearing the corresponding **UAE** bit in the User Address Enable Packet before changing any of the bits in the corresponding User Address Assignment Packet. This method allows for easy reprogramming of user addresses without disrupting normal operation. The IDs for these packets range from 128 to 143 (decimal).

|        | Bit 7           | Bit 6           | Bit 5           | Bit 4           | Bit 3           | Bit 2           | Bit 1           | Bit 0           |

|--------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Byte 3 | 1               | 0               | 0               | 0               | a <sub>3</sub>  | a <sub>2</sub>  | a₁              | $a_0$           |

| Byte 2 | 0               | LA              | TOA             | A <sub>20</sub> | A <sub>19</sub> | A <sub>18</sub> | A <sub>17</sub> | A <sub>16</sub> |

| Byte 1 | A <sub>15</sub> | A <sub>14</sub> | A <sub>13</sub> | A <sub>12</sub> | A <sub>11</sub> | A <sub>10</sub> | A <sub>9</sub>  | A <sub>8</sub>  |

| Byte 0 | A <sub>7</sub>  | A <sub>6</sub>  | A <sub>5</sub>  | A <sub>4</sub>  | A <sub>3</sub>  | A <sub>2</sub>  | A <sub>1</sub>  | A <sub>0</sub>  |

#### Table 18: User Address Assignment Packet Bit Assignments

- a: User Address Word Number. This specifies which address word is being configured. A zero in this field corresponds to address index zero (**Al**=0) in the Address Packet received from the S5T8702 when an address is detected. See <u>"Address Packet" on page 36</u> for a description of the address index field.

- LA: Long address. When this bit is set, the address is considered a long address. Both words of a long address must have this bit set. The first word of a long address must have an even address index and the second word must be in the address index immediately following the first word.

- **TOA:** Tone-Only Address. When this bit is set, the S5T8702 will consider this address a tone-only address and will not decode a vector word when the address is received. If the **TOA** bit of a long address word is set, the **TOA** bit of the other word of the long address must also be set.

- A: Address word. This is the 21 bit value of the address word. Valid FLEX messaging addresses or Network ID's may be used.

## **DECODER-TO-HOST PACKET DESCRIPTIONS**

The following sections describe the packets of information that will be sent from the S5T8702 to the host. In all cases the packets are sent MSB first (bit 7 of byte 3 = bit 31 of the packet = MSB). The S5T8702 decides what data should be sent to the host. If the S5T8702 is disabled through the checksum feature (see <u>"Checksum Packet" on page 16</u> for a description of the checksum feature) the Part ID Packet will be sent. Data Packets relating to data received over the air are buffered in the 32 packet transmit buffer. The Data packets include Block Information Word Packets, Address Packets, Vector Packets, and Message Packets.

If the S5T8702 is enabled and a receiver shutdown packet is pending, the receiver shutdown packet will be sent. If there is no receiver shutdown packet pending, but there is a roaming status packet pending, the roaming status packet will be sent. If neither the receiver shutdown packet nor the roaming status packet is pending and there is data in the transmit buffer, a packet from the transmit buffer will be sent. Otherwise, the S5T8702 will send the Status Packet (which is not buffered). In the event of a buffer overflow, the S5T8702 will automatically stop decoding and clear the buffer.

It is recommended that the Host be designed to empty the FIFO buffer every block with enough time left over to read a status packet. This would ensure that any applicable Status Packet would be received within 1 block of the new status being available.

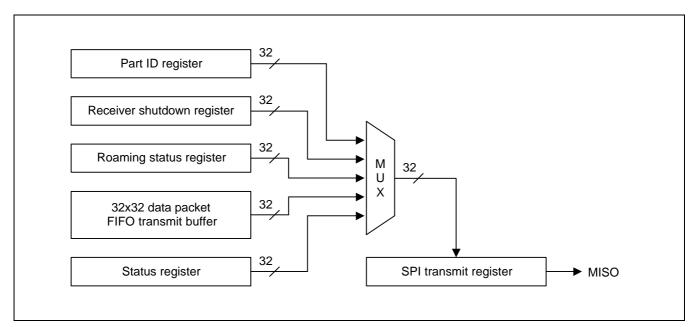

Figure 10: FLEX decoder IC SPI Transmit Functional Block Diagram

## **BLOCK INFORMATION WORD PACKET**

The Block Information Field is the first field following the synchronization codes of the FLEX protocol. This field contains information about the frame such as number of addresses and messages, information about current time, the channel ID, channel attributes, etc. The first block information word of each phase is used internally to the S5T8702 and is never transmitted to the host with the exception of the system collapse which is sent to the host when the S5T8702 is in manual collapse mode.

Time block information words 2-4 can be optionally sent to the host by setting the **SBI** bit in the control packet (see <u>"Control Packet" on page 21</u>). All block information words 2-4 can be optionally sent to the host by setting the **ABI** bit in the roaming control packet. When the **SBI** or **ABI** bit is set and any block information word 2-4 is received with an uncorrectable number of bit errors, the S5T8702 will send the block information word to the host with the e bit set regardless of the value of the f field in the block information word. The S5T8702 does not support decoding of the vector and message words associated with the Data/System Message block info word (**f**=101). The ID of a Block Information Word Packet is 0 (decimal).

|        | Bit 7                 | Bit 6          | Bit 5                  | Bit 4                  | Bit 3           | Bit 2                  | Bit 1          | Bit 0          |

|--------|-----------------------|----------------|------------------------|------------------------|-----------------|------------------------|----------------|----------------|

| Byte 3 | 0                     | 0              | 0                      | 0                      | 0               | 0                      | 0              | 0              |

| Byte 2 | е                     | p <sub>1</sub> | p <sub>0</sub>         | х                      | х               | f <sub>2</sub>         | f <sub>1</sub> | f <sub>0</sub> |

| Byte 1 | х                     | х              | <b>S</b> <sub>13</sub> | <b>S</b> <sub>12</sub> | S <sub>11</sub> | <b>S</b> <sub>10</sub> | S <sub>9</sub> | S <sub>8</sub> |

| Byte 0 | <b>S</b> <sub>7</sub> | S <sub>6</sub> | $S_5$                  | S <sub>4</sub>         | S <sub>3</sub>  | S <sub>2</sub>         | S <sub>1</sub> | <b>S</b> 0     |

#### **Table 19: Block Information Word Packet Bit Assignments**

- e: Set if more than 2 bit errors are detected in the word or if the check character calculation fails after error correction has been performed.

- **p:** Phase on which the block information word was found (0=a, 1=b, 2=c, 3=d)

- **x:** Unused bits. The value of these bits is not guaranteed.

- f: Word Format Type. The value of these bits modify the meaning of the s bits in this packet as described in the BIW word descriptions in the s bit definition below.

s:

These are the information bits of the block information word. The definition of these bits depend on the f bits in this packet. The following table describes the block information words.

| $f_2 f_1 f_0$    | <b>S</b> 13    | <b>S</b> 12                                | <b>S</b> <sub>11</sub> | <b>S</b> 10    | S <sub>9</sub> | S <sub>8</sub> | <b>S</b> 7     | S <sub>6</sub> | <b>S</b> 5     | S <sub>4</sub> | S <sub>3</sub> | S <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub>        | Description                               |

|------------------|----------------|--------------------------------------------|------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------------|-------------------------------------------|

| 000 <sup>a</sup> | i <sub>8</sub> | i7                                         | i <sub>6</sub>         | i <sub>5</sub> | İ4             | İ3             | i <sub>2</sub> | İ1             | i <sub>o</sub> | $C_4$          | C <sub>3</sub> | C <sub>2</sub> | C <sub>1</sub> | <b>C</b> <sub>0</sub> | Local ID, Coverage Zone                   |

| 001 <sup>b</sup> | m <sub>3</sub> | m <sub>2</sub>                             | m₁                     | $m_0$          | $d_4$          | d <sub>3</sub> | d <sub>2</sub> | d1             | $d_0$          | $Y_4$          | $Y_3$          | $Y_2$          | $Y_1$          | Y <sub>0</sub>        | Month ,Day, Year                          |

| 010 <sup>b</sup> | S <sub>2</sub> | S <sub>1</sub>                             | S <sub>0</sub>         | $M_5$          | $M_4$          | $M_3$          | $M_2$          | $M_1$          | $M_0$          | $H_4$          | $H_3$          | $H_2$          | H <sub>1</sub> | H₀                    | Second ,Minute, Hour                      |

| 011 <sup>a</sup> | Rese           | Reserved by FLEX protocol for future use   |                        |                |                |                |                |                |                |                |                |                |                |                       |                                           |

| 100 <sup>a</sup> | Rese           | erved b                                    | by FLE                 | EX pro         | tocol f        | for futu       | ure us         | е              |                |                |                |                |                |                       |                                           |

| 101 <sup>b</sup> | Z <sub>9</sub> | Z <sub>8</sub>                             | <b>Z</b> 7             | Z <sub>6</sub> | <b>Z</b> 5     | <b>Z</b> 4     | Z <sub>3</sub> | <b>Z</b> 2     | <b>Z</b> 1     | Z <sub>0</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub>        | System Message                            |

| 110 <sup>a</sup> | Rese           | erved b                                    | by FLE                 | EX pro         | tocol          | for futu       | ure us         | е              |                |                |                |                |                |                       |                                           |

| 111 <sup>a</sup> | C9             | C8                                         | C7                     | <b>C</b> 6     | <b>C</b> 5     | <b>C</b> 4     | C3             | <b>C</b> 2     | C <sub>1</sub> | <b>C</b> 0     | T <sub>3</sub> | T <sub>2</sub> | T <sub>1</sub> | T <sub>0</sub>        | Country Code, Traffic<br>Management Flags |

| a.               |                | Will be decoded only if the ABI bit is set |                        |                |                |                |                |                |                |                |                |                |                |                       |                                           |

| h-               |                | 14/:11                                     | ما م                   |                | با مرم ا       | . :            |                |                |                |                |                |                |                |                       |                                           |

b. Will be decoded only if the **SBI** or **ABI** bit is set

# ADDRESS PACKET

The Address Field follows the Block Information Field in the FLEX protocol. It contains all of the address in the frame.

If less than three bit errors are detected in a received address word and it matches an enabled address assigned to the S5T8702, an Address Packet will be sent to the host processor. The Address Packet contains assorted data about the address and its associated vector and message. The ID of an Address Packet is 1 (decimal).

|        | Bit 7           | Bit 6           | Bit 5           | Bit 4           | Bit 3  | Bit 2  | Bit 1           | Bit 0           |

|--------|-----------------|-----------------|-----------------|-----------------|--------|--------|-----------------|-----------------|

| Byte 3 | 0               | 0               | 0               | 0               | 0      | 0      | 0               | 1               |

| Byte 2 | PA              | p <sub>1</sub>  | p <sub>0</sub>  | LA              | х      | х      | х               | х               |

| Byte 1 | Al <sub>7</sub> | Al <sub>6</sub> | Al <sub>5</sub> | $AI_4$          | $AI_3$ | $AI_2$ | AI <sub>1</sub> | Al <sub>0</sub> |

| Byte 0 | TOA             | WN <sub>6</sub> | WN <sub>5</sub> | WN <sub>4</sub> | $WN_3$ | $WN_2$ | WN <sub>1</sub> | WN <sub>0</sub> |

#### Table 20: Address Packet Bit Assignments

**PA:** Priority Address. Set if the address was received as a priority address.

**p:** Phase on which the address was detected (0=a, 1=b, 2=c, 3=d)

- AI: Address Index (valid values are 0 through 15 and 128 through 159). The index identifies which of the addresses was detected. Values 0 through 15 correspond to the 16 programmable address words. Values 128 through 143 correspond to the 16 temporary addresses. Values 144 through 159 correspond to the 16 operator messaging addresses. For long addresses, the address detect packet will only be sent once and the index will refer to the second word of the address.

- **TOA:** Tone Only Address. Set if the address was programmed in the S5T8702 as a tone-only address. This bit will never be set for temporary or operator messaging addresses. No vector word will be sent for tone-only addresses.

- **WN:** Word number of vector (2 87). Describes the location in the frame of the vector word for the detected address. This value is invalid for this packet if the TOA bit is set.

- **x:** Unused bits. The value of these bits is not guaranteed.

LA: Long Address type. Set if the address was programmed in the S5T8702 as a long address.

## **VECTOR PACKET**

The Vector Field follows the Address Field in the FLEX protocol. Each Vector Packet must be matched to its corresponding Address Packet. The ID of the vector packet is the word number where the vector word was received in the frame. This value corresponds to the **WN** bits sent in the associated address packet. The phase information in both the Address Packet and the Vector Packet must also match. It is important to note for long addresses, the first message word will be transmitted in the word location immediately following the associated vector. See <u>"Message Building" on page 59</u> for a message building example. In this case, the word number (identified by **b**<sub>6</sub> to **b**<sub>0</sub>) in the Vector Packet will indicate the message start of the second message word if the message is longer than 1 word.

There are several types of vectors - 3 types of Numeric Vectors, a Short Message / Tone Only Vector, a Hex / Binary Vector, an Alphanumeric Vector, a Secure Message Vector, and a Short Instruction Vector. Each is described in the following pages. One of the modes of the Short Instruction Vector is used for assigning temporary addresses that may be associated with a group call.

The Numeric, Hex / Binary, Alphanumeric, and Secure Message Vector Packets have associated Message Word Packets in the message field. The host must use the  $\mathbf{n}$  and  $\mathbf{b}$  bits of the vector word to calculate what message word locations are associated with the vector. Both the message word locations and the phase must match.

Four of the vectors (Hex / Binary, Alphanumeric, Secure Message, and Short Instruction) enable the S5T8702 to begin the all frame mode. This mode is required to allow for the decoding of temporary addresses and / or fragmented messages. The host disables the All Frame Mode after the proper time by writing to the decoder via the All Frame Mode Packet. See <u>"Building a Fragmented Message" on page 54</u> and <u>"Operation of a Temporary Address" on page 57</u> for more information. For any Address Packet sent to the host (except tone-only addresses), a corresponding Vector Packet will always be sent. If more than two bit errors are detected (via BCH calculations, parity calculations, check character calculations, or value validation) in the vector word the e bit will be set and the message words will not be sent.

## NUMERIC VECTOR PACKET

|        | Bit 7          | Bit 6           | Bit 5          | Bit 4          | Bit 3          | Bit 2          | Bit 1           | Bit 0          |

|--------|----------------|-----------------|----------------|----------------|----------------|----------------|-----------------|----------------|

| Byte 3 | 0              | WN <sub>6</sub> | $WN_5$         | $WN_4$         | $WN_3$         | $WN_2$         | WN <sub>1</sub> | $WN_0$         |

| Byte 2 | е              | p <sub>1</sub>  | p <sub>0</sub> | х              | х              | V <sub>2</sub> | V <sub>1</sub>  | V <sub>0</sub> |

| Byte 1 | х              | х               | K <sub>3</sub> | K <sub>2</sub> | K <sub>1</sub> | K <sub>0</sub> | n <sub>2</sub>  | n <sub>1</sub> |

| Byte 0 | n <sub>o</sub> | b <sub>6</sub>  | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub>  | b <sub>0</sub> |

### Table 21: Numeric Vector Packet Bit Assignments

## V: Vector type identifier.

| $V_2 V_1 V_0$ | Name                             | Description                                                                                                             |

|---------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 011           | Standard Numeric Vector          | No special formatting of characters is specified                                                                        |

| 100           | Special Format Numeric<br>Vector | Formatting of the received characters is predetermined by special rules in the host.                                    |

| 1 1 1         | Numbered Numeric Vector          | The received information has been numbered by the service provider to indicate all messages have been properly received |

- WN: Word number of vector (2 87 decimal). Describes the location of the vector word in the frame.

- e: Set if more than 2 bit errors are detected in the word, if the check character calculation fails after error correction has been performed, or if the vector value is determined to be invalid.

- p: Phase on which the vector was found (0=a, 1=b,2=c, 3=d)

- K: Beginning check bits of the message.

- **n:** Number of message words in the message including the second vector word for long addresses (000=1 word message, 001=2 word message, etc.). For long addresses, the first message word is located in the word location that immediately follows the associated vector.

- **b:** Word number of message start in the message field (3 87 decimal). For long addresses, the word number indicates the location of the second message word.

- **x:** Unused bits. The value of these bits is not guaranteed.

# SHORT MESSAGE / TONE ONLY VECTOR